tified)

MAHARASHTF (Autonomous) (ISO/IEC - 2700

## WINTER - 19EXAMINATION

Subject Code: 22426

Subject Name: Microcontroller & Application Model Answer

## Important Instructions to examiners:

- 1) The answers should be examined by key words and not as word-to-word as given in themodel answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may tryto assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q. N. |                                                                        | Ansv                                                                                                                                                                 | ver                                                  | Marking<br>Scheme             |

|-----------|--------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|

| Q.1       |              | Attempt any FI                                                         | VE of the following:                                                                                                                                                 |                                                      | 10M                           |

|           | <b>a</b> )   | Compare addres                                                         | s bus and data bus used in 8                                                                                                                                         | 051.                                                 | 2M                            |

|           | Ans:         | Sr. No.                                                                | Address Bus                                                                                                                                                          | Data Bus                                             | 1M each                       |

|           |              | 1                                                                      | A bus that is used to<br>specify a physical address<br>in memory                                                                                                     | A bus that is used to transmit data among components | (Any 2<br>points)             |

|           |              | 2                                                                      | Unidirectional                                                                                                                                                       | Bidirectional                                        |                               |

|           |              | 3                                                                      | Helps to transfer memory address of data and I/O                                                                                                                     | Helps to send and receive data                       |                               |

|           |              | 4                                                                      | 16 bit address bus in 8051                                                                                                                                           | 8 bit data bus in 8051                               |                               |

|           | <b>b</b> )   | Calculate the nu                                                       | mber of address lines requir                                                                                                                                         | ed to access 16 kB ROM.                              | <b>2M</b>                     |

|           | Ans:         | 14 address lines re<br>2 $^{14} = 16$ KB                               | equired to access 16 KB of RC                                                                                                                                        | DM as                                                | 2M                            |

|           | c)           | State features of                                                      | ADC 0808.                                                                                                                                                            |                                                      | 2M                            |

|           | Ans:         | <ol> <li>Eight char</li> <li>Can measure</li> <li>On chip C</li> </ol> | terface with all Microprocesson<br>nnel 8-bit <b>ADC</b> module.<br>ure up to 8 Analog values.<br>Clock not available, external Os<br>tput various from 0 to 255, op |                                                      | 1M each<br>( Any 2<br>points) |

|           | <b>d</b> )   | List specification                                                     | ns of 8051 microcontroller.                                                                                                                                          |                                                      | 2M                            |

|           | Ans:         | 1) 8- bit data                                                         | bus and 8- bit ALU.                                                                                                                                                  |                                                      | 1M each                       |

|           |              | 2) 16- bit add                                                         | dress bus – can access maximu                                                                                                                                        | m 64KB of RAM and ROM.                               | ( Any 2                       |

|           |              | 3) On- chip I                                                          | RAM -128 bytes (Data Memor                                                                                                                                           | y)                                                   | points)                       |

|           |              | 4) On- chip I                                                          | ROM – 4 KB (Program Memo                                                                                                                                             | ry)                                                  |                               |

|            | ports.<br>6) Progr<br>7) Two<br>8) Work<br>9) Has p<br>10) Six in                                                                  | ammable serial ports i.e. One UAR'<br>6- bit timers- Timer 0& Timer 1<br>s on crystal frequency of 11.0592 M                                                                                                                                                      | 1Hz<br>controller when no operation is perfor                                                                |                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------|

| e)<br>Ans: | MOV A,#001<br>CLR A                                                                                                                |                                                                                                                                                                                                                                                                   | ulator zero murvidualiy.                                                                                     | 2M<br>1M each                         |

| <b>f</b> ) | Compare da                                                                                                                         | ta memory and program memory                                                                                                                                                                                                                                      | 7.                                                                                                           | 2M                                    |

| Ans:       | Sr.N                                                                                                                               | o. Program Memory                                                                                                                                                                                                                                                 | Data Memory                                                                                                  | 1M each                               |

|            | 1                                                                                                                                  | It is used for storing<br>the hexadecimal codes of the<br>program to be executed i.e.<br>instructions.<br>Program Memory of 8051 is                                                                                                                               | It is used for storing temporary<br>variable data and intermediate<br>results.<br>Data Memory of 8051 is 128 |                                       |

|            | 2                                                                                                                                  | 4kB                                                                                                                                                                                                                                                               | bytes                                                                                                        |                                       |

| <b>g</b> ) | List SFR in                                                                                                                        | 8051. (any four)                                                                                                                                                                                                                                                  |                                                                                                              | 2M                                    |

| Ans:       | <ul> <li>DPTF</li> <li>PC : I</li> <li>Stack</li> <li>PSW</li> <li>Port I</li> <li>Serial</li> <li>Timer</li> <li>Power</li> </ul> | and B registers – 8 bit each<br>: [DPH:DPL] – 16 bit combined<br>Program Counter – 16 bits<br>pointer SP – 8 bit<br>: Program Status Word<br>atches<br>data buffer, serial control<br>Registers (TCON,TMOD,TL0/1,T<br>· control<br>upt Enable, Interrupt Priority | Ή0/1)                                                                                                        | <sup>1</sup> / <sub>2</sub> M<br>each |

|     |      |                                   |             |               |               |          |                   |                 | 12-        |

|-----|------|-----------------------------------|-------------|---------------|---------------|----------|-------------------|-----------------|------------|

| Q.2 |      | Attempt any THRE                  | E of the f  | following:    |               |          |                   |                 | Total      |

|     |      |                                   |             |               |               |          |                   |                 | Mark       |

|     | a)   | Compare any three and Interrupts. | derivativ   | es of 8051 m  | icrocontr     | oller on | the basis of      | RAM,ROM,Timer   | <b>4</b> M |

|     | Ans: | Features                          | 8051        | 8052          | 89c52         | 8031     | 8751              | 89v51 RD2       | 1M<br>each |

|     |      | RAM                               | 128         | 256           | 256           | 128      | 128               | 1k              | (Any<br>4  |

|     |      | ROM                               | 4K<br>(mask | 8K<br>(EPROM) | 8K<br>(Flash) | 0        | 4K (UV-<br>EPROM) | 64KB<br>(FLASH) | Points     |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROM)                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |                                                                                                                                                                                  |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                    |                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|            | TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                            | 3                                                                                                                                                                                                | 2                                                                                                                                                                                | 2                                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                  |                   |

|            | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                                                         | 8                                                                                                                                                                                                                                                                            | 8                                                                                                                                                                                                | 6                                                                                                                                                                                | 6                                                                                                                                                                                                         | 8                                                                                                                                                                                                                                                                  |                   |

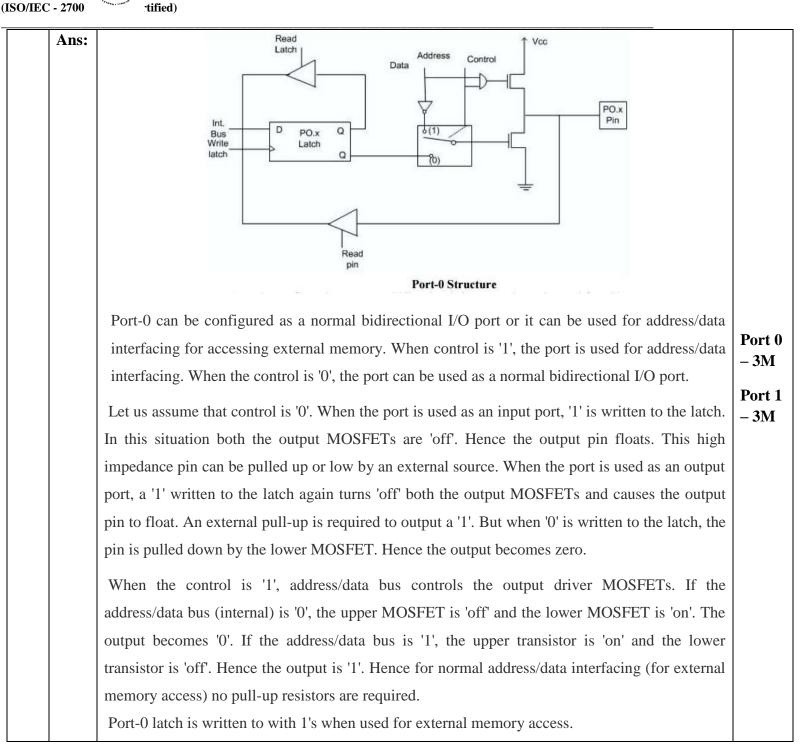

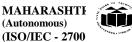

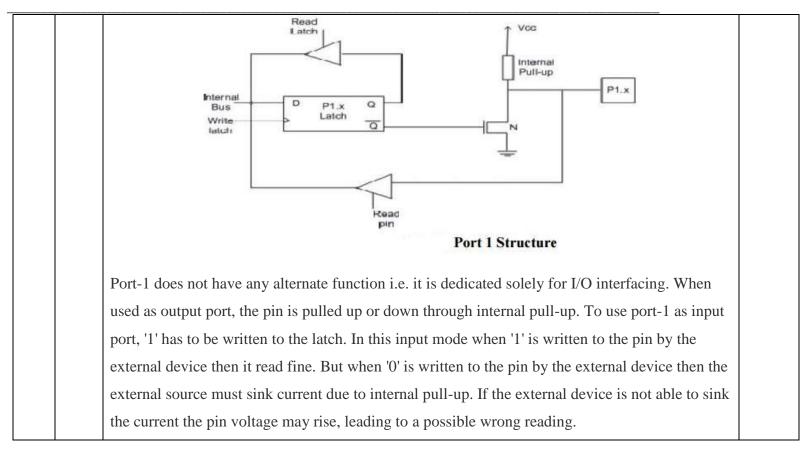

| b)         | Draw and explain th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e interfa                                                                                                                                                                                                                                                 | cing of DAC                                                                                                                                                                                                                                                                  | to 8051.                                                                                                                                                                                         | <u> </u>                                                                                                                                                                         |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                    | <b>4</b> M        |

| Ans:       | Diagram:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |                                                                                                                                                                                  |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                    | 2M                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2<br>7<br>V<br>v<br>v<br>v                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                            | $3^{5k}$                                                                                                                                                                                         | ligital for                                                                                                                                                                      | 1k<br>0.1uF                                                                                                                                                                                               | TO<br>SCOPE<br>Vout = 0<br>to 10V                                                                                                                                                                                                                                  | 2M                |

|            | <ul><li>DAC which co</li><li>In the figure sh equivalent ana</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | onverts di<br>nown, we<br>log currer                                                                                                                                                                                                                      | gital data int<br>use 8-bit DA<br>nt. Hence we                                                                                                                                                                                                                               | o equivale<br>AC 0808. '                                                                                                                                                                         | ent analog<br>This IC co                                                                                                                                                         | g voltage.<br>onverts 8 bi                                                                                                                                                                                | it necessary to use<br>t digital data into<br>convert this current                                                                                                                                                                                                 | -                 |

|            | <ul> <li>DAC which co</li> <li>In the figure sh<br/>equivalent ana<br/>into equivalent</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | onverts di<br>nown, we<br>log curren<br>t voltage.                                                                                                                                                                                                        | gital data int<br>use 8-bit DA<br>nt. Hence we                                                                                                                                                                                                                               | o equivale<br>AC 0808. '<br>require a                                                                                                                                                            | ent analog<br>This IC co<br>n I to V c                                                                                                                                           | g voltage.<br>onverts 8 bi                                                                                                                                                                                | t digital data into                                                                                                                                                                                                                                                | natio             |

| c)         | DAC which co<br>In the figure sh<br>equivalent ana<br>into equivalent<br>Describe 8051 micro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | onverts di<br>nown, we<br>log curren<br>t voltage.<br><b>controlle</b>                                                                                                                                                                                    | gital data int<br>use 8-bit DA<br>nt. Hence we<br>r as boolean                                                                                                                                                                                                               | o equivale<br>AC 0808. '<br>require a<br><b>processo</b>                                                                                                                                         | ent analog<br>This IC co<br>n I to V c<br>or.                                                                                                                                    | g voltage.<br>onverts 8 bi<br>converter to                                                                                                                                                                | t digital data into<br>convert this current                                                                                                                                                                                                                        | natio             |

| c)<br>Ans: | <ul> <li>DAC which co</li> <li>In the figure sh<br/>equivalent and<br/>into equivalent</li> <li>Describe 8051 micro</li> <li>8051 processor</li> <li>The 8051 processor</li> <li>The internal R<br/>other addressa</li> <li>All port lines a</li> <li>The instruction<br/>complete set o</li> <li>The 8051 instruction<br/>provides direct<br/>single bit varia<br/>Boolean expre</li> <li>Eg: CLR C media</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | onverts di<br>nown, we<br>log current<br>t voltage.<br><b>controlle</b><br>r is a CPU<br>cessor cont<br>AM cont<br>ble bits.<br>are bit-ado<br>ns that a<br>f move, s<br>ruction set<br>t support<br>table to p<br>ssion. Bit<br>eans clear               | gital data intr<br>use 8-bit DA<br>nt. Hence we<br>r as boolean<br>J that can per<br>ntains a comp<br>tains 128 add<br>dressable, an<br>access these<br>et, clear, con<br>et is optimize<br>for bit manip<br>perform logid<br>ts may be set<br>the carry bit                 | o equivale<br>AC 0808.7<br>require a<br><b>processo</b><br>rform som<br>plete Bool<br>hressable h<br>d each can<br>bits are<br>plement,<br>ed for the<br>pulation an<br>cal operat<br>or cleared | ent analog<br>This IC con<br>n I to V con<br>or.<br>The operative<br>ean proceed<br>bits, and the<br>not only<br>OR, and<br>one bit on<br>not testing<br>ions there<br>i na sing | g voltage.<br>onverts 8 bit<br>onverter to<br>on on a data<br>essor for sin<br>the SFR spa-<br>ed as a separ<br>conditiona<br>AND instru-<br>perations. To<br>of individu<br>efore 8051<br>gle instructio | t digital data into<br>convert this current<br>a and gives the output.<br>gle-bit operations.<br>ace supports up to 128<br>rate single-bit port.<br>l branches but also a<br>actions.<br>The Boolean processor<br>al bit allows the use of<br>can be used to solve | natio             |

| ,          | <ul> <li>DAC which co</li> <li>In the figure sh<br/>equivalent and<br/>into equivalent</li> <li>Describe 8051 micro</li> <li>8051 processor</li> <li>The 8051 processor</li> <li>The internal R<br/>other addressar</li> <li>All port lines a</li> <li>The instruction<br/>complete set o</li> <li>The 8051 instru-<br/>provides direct<br/>single bit varia</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | onverts di<br>hown, we<br>log current<br>t voltage.<br><b>controlle</b><br>r is a CPU<br>cessor cont<br>AM cont<br>ble bits.<br>are bit-add<br>ns that a<br>f move, s<br>ruction set<br>t support<br>able to p<br>ssion. Bit<br>eans clear<br>ans set the | gital data intr<br>use 8-bit DA<br>nt. Hence we<br>r as boolean<br>J that can per<br>ntains a comp<br>cains 128 add<br>dressable, an<br>access these<br>et, clear, con<br>et is optimize<br>for bit manip<br>perform logic<br>ts may be set<br>the carry bit<br>e memory bit | o equivale<br>AC 0808.7<br>require a<br>processo<br>rform som<br>plete Bool<br>d each can<br>bits are<br>aplement,<br>ed for the<br>pulation ar<br>cal operat<br>or cleared                      | ent analog<br>This IC con<br>n I to V con<br>or.<br>The operative<br>ean proceed<br>bits, and the<br>not only<br>OR, and<br>one bit on<br>not testing<br>ions there<br>i na sing | g voltage.<br>onverts 8 bit<br>onverter to<br>on on a data<br>essor for sin<br>the SFR spa-<br>ed as a separ<br>conditiona<br>AND instru-<br>perations. To<br>of individu<br>efore 8051<br>gle instructio | t digital data into<br>convert this current<br>a and gives the output.<br>gle-bit operations.<br>ace supports up to 128<br>rate single-bit port.<br>l branches but also a<br>actions.<br>The Boolean processor<br>al bit allows the use of<br>can be used to solve | natio             |

| Ans:       | <ul> <li>DAC which co</li> <li>In the figure she equivalent and into equivalent and into equivalent</li> <li>Boscribe 8051 micro</li> <li>8051 processor</li> <li>The 8051 processor</li> <li>The internal R other addressar</li> <li>All port lines a</li> <li>The instruction complete set or</li> <li>The 8051 instruction complete set or</li> <li>The 8051 instruction generation of the set of the set</li></ul> | onverts di<br>hown, we<br>log current<br>t voltage.<br><b>controlle</b><br>r is a CPU<br>cessor cont<br>AM cont<br>ble bits.<br>are bit-add<br>ns that a<br>f move, s<br>ruction set<br>t support<br>able to p<br>ssion. Bit<br>eans clear<br>ans set the | gital data intr<br>use 8-bit DA<br>nt. Hence we<br>r as boolean<br>J that can per<br>ntains a comp<br>cains 128 add<br>dressable, an<br>access these<br>et, clear, con<br>et is optimize<br>for bit manip<br>perform logic<br>ts may be set<br>the carry bit<br>e memory bit | o equivale<br>AC 0808.7<br>require a<br>processo<br>rform som<br>plete Bool<br>d each can<br>bits are<br>aplement,<br>ed for the<br>pulation ar<br>cal operat<br>or cleared                      | ent analog<br>This IC co<br>n I to V c<br>or.<br>ne operative<br>ean proceed<br>bits, and the<br>not only<br>OR, and<br>one bit on<br>nd testing<br>ions there<br>I in a sing    | g voltage.<br>onverts 8 bit<br>onverter to<br>on on a data<br>essor for sin<br>the SFR spa-<br>ed as a separ<br>conditiona<br>AND instru-<br>perations. To<br>of individu<br>efore 8051<br>gle instructio | t digital data into<br>convert this current<br>a and gives the output.<br>gle-bit operations.<br>ace supports up to 128<br>rate single-bit port.<br>l branches but also a<br>actions.<br>The Boolean processor<br>al bit allows the use of<br>can be used to solve | antic<br>4M<br>4M |

| Ans:       | <ul> <li>DAC which co</li> <li>In the figure sh<br/>equivalent ana<br/>into equivalent</li> <li>Describe 8051 micro</li> <li>8051 processor</li> <li>The 8051 processor</li> <li>The internal R<br/>other addressa</li> <li>All port lines a</li> <li>The instruction<br/>complete set o</li> <li>The 8051 instruction<br/>provides direct<br/>single bit vari<br/>Boolean expre</li> <li>Eg: CLR C me<br/>SETB 20h mea</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | onverts di<br>hown, we<br>log current<br>t voltage.<br><b>controlle</b><br>r is a CPU<br>cessor cont<br>AM cont<br>ble bits.<br>are bit-add<br>ns that a<br>f move, s<br>ruction set<br>t support<br>able to p<br>ssion. Bit<br>eans clear<br>ans set the | gital data intr<br>use 8-bit DA<br>nt. Hence we<br>r as boolean<br>J that can per<br>ntains a comp<br>cains 128 add<br>dressable, an<br>access these<br>et, clear, con<br>et is optimize<br>for bit manip<br>perform logic<br>ts may be set<br>the carry bit<br>e memory bit | o equivale<br>AC 0808.7<br>require a<br>processo<br>rform som<br>plete Bool<br>d each can<br>bits are<br>aplement,<br>ed for the<br>pulation ar<br>cal operat<br>or cleared                      | ent analog<br>This IC co<br>n I to V c<br>or.<br>ne operative<br>ean proceed<br>bits, and the<br>not only<br>OR, and<br>one bit on<br>nd testing<br>ions there<br>I in a sing    | g voltage.<br>onverts 8 bit<br>onverter to<br>on on a data<br>essor for sin<br>the SFR spa-<br>ed as a separ<br>conditiona<br>AND instru-<br>perations. 7<br>of individu<br>efore 8051<br>gle instructio  | t digital data into<br>convert this current<br>a and gives the output.<br>gle-bit operations.<br>ace supports up to 128<br>rate single-bit port.<br>l branches but also a<br>actions.<br>The Boolean processor<br>al bit allows the use of<br>can be used to solve |                   |

**BOARD OF TECHNICAL EDUCATION**

|      | <ul> <li>then it access internal and external program memories (ROMS).</li> <li>ii) Pin 29- PSEN : This is an output pin. PSEN stands for "program store enable." It is active low O/P signal. It is used to enable external program memory (ROM). When [PSEN(bar)]= 0, then external program memory becomes enabled and micro controller read content of external memory location. Therefore it is connected to (OE) of external ROM.</li> <li>iii) Pin 21-28: A<sub>8</sub> - A<sub>15</sub> : These pins are known as Port 2. It serves as I/O port. Each pin is bidirectional Input /Output with internal pull – up resistors. Besides the Input /Output, when external memory is interfaced, PORT 2 pins act as the higher-order address bus. (A8-A15)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1M-<br>PSEN<br>2M-Pin<br>21-28<br>1M<br>Port 2<br>& 1M<br>A8 -<br>A15 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Q.3  | Attempt any THREE of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12-<br>Total<br>Marks                                                 |

| a)   | Develop Assembly Language program (ALP) to find the largest number in a block of 10<br>numbers stored at location 40H onwards in internal RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>4</b> M                                                            |

| Ans: | (NOTE: Marks to be given for any other correct logic used by students.)         ORG 0000H         MOV R1, #0AH       ; Initialize Byte Counter         MOV R0, #40H       ; Initialize source pointer R0 to 40H         DEC R1       ; decrement counter by one         MOV 60H, @R0       ; Read First Byte         UP: INC R0       ; Increment the contents of R0         MOV A, @R0       ; Read second number         CJNE A, 60H, DN       ; compare the first two numbers, if not equal go to DN         AJMP LARGE       ; else go to LARGE         DN: JC LARGE       ; check carry         MOV 60H, A       ; Store largest number to 60H         LARGE: DJNZ R1, UP       ; decrement the counter by one, if count ≠ 0, then go to UP         END       Largest No. is saved in memory 60H. Assume any location to store the result.         OR         MOV R1, #0AH       ; initialize the counter         MOV R0, #40H       ; initialize the memory pointer         DEC R1       ; decrement counter by one         MOV A,@R0       ; load number in accumulator         MOV B, A       ; move that number to register B         UP: INC R0       ; increment the memory pointer         DAG       ; else go to NEXT         MOV B, A       ; else go to NEXT <tr< th=""><th>4M<br/>for<br/>correc<br/>t<br/>progr<br/>am</th></tr<> | 4M<br>for<br>correc<br>t<br>progr<br>am                               |

| b)         | Sketch the internal memory organization in 8051.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>4</b> M                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Ans:       | Daigram:       Byte<br>Address     Bit address       Byte<br>Address     Bit address       Byte<br>Address     Bit address       TFh     General purpose<br>RAM area.<br>80 bytes       30h     Internal Memory       2Eh $\overline{77}$ $\overline{78}$ 2Dh $\overline{67}$ $\overline{68}$ 2Ch $\overline{57}$ $\overline{50}$ 2Dh $\overline{17}$ $\overline{10}$ 2Bh $\overline{17}$ $\overline{18}$ 2Dh $\overline{17}$ $\overline{18}$ 2Dh $\overline{07}$ $\overline{88}$ $2Dh$ $\overline{67}$ $\overline{68}$ $2Dh$ $\overline{77}$ $\overline{38}$ $2Dh$ $\overline{17}$ $\overline{18}$ $2Dh$ $\overline{67}$ $2Dh$ $\overline{67}$ | 4M<br>for<br>neat<br>Sketo<br>h wit<br>label |

| c)<br>Ans: | <ul> <li>Explain processes of interrupt enabling and disabling in 8051.</li> <li>Interrupts are the events that temporarily suspend the main program, pass the control to the external sources and execute their task. It then passes the control to the main program where it had left off.8051 has 5 interrupt signals, i.e. INTO, TFO, INT1, TF1, RI/TI. Each interrupt can be enabled or disabled by setting bits of the IE register and the whole interrupt system can be disabled by clearing the EA bit of the same register.</li> <li>IE (Interrupt Enable) Register:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                | 4M<br>2M<br>form<br>t                        |

|            | This register is responsible for enabling and disabling the interrupt. EA bit is set to 1 for enabling interrupts and set to 0 for disabling the interrupts. Its bit sequence and their meanings are shown in the following figure.         EA       _       _       ES       ET1       EX1       ET0       EX0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

|            | EA          | IE.7        | It disables all interrupts. When EA = 0 no interrupt will be acknowledged and EA = 1 enables the interrupt individually.                               | bit        |

|------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | -           | IE.6        | Reserved for future use.                                                                                                                               |            |

|            | -           | IE.5        | Reserved for future use.                                                                                                                               |            |

|            | ES          | IE.4        | Enables/disables serial port interrupt.                                                                                                                |            |

|            | ET1         | IE.3        | Enables/disables timer1 overflow interrupt.                                                                                                            |            |

|            | EX1         | IE.2        | Enables/disables external interrupt1.                                                                                                                  |            |

|            | ET0         | IE.1        | Enables/disables timer0 overflow interrupt.                                                                                                            |            |

|            | EX0         | IE.0        | Enables/disables external interrupt0.                                                                                                                  |            |

|            | Explain     |             | g instructions of 8051.                                                                                                                                |            |

| <b>d</b> ) | (i)         | ADDO        |                                                                                                                                                        | <b>4</b> M |

|            | (ii)        | L CA        |                                                                                                                                                        |            |

| Ans:       | (i)         |             | C: The <b>ADDC</b> instruction adds a byte value and the value of the carry flag to                                                                    | <b>2M</b>  |

|            |             |             | cumulator. The results of the addition are stored back in the accumulator.                                                                             | each       |

|            |             | Severa      | al of the flag registers are affected.                                                                                                                 | instr      |

|            | ADDC        |             |                                                                                                                                                        | ction      |

|            | Function    |             | •                                                                                                                                                      |            |

|            | -           |             | , source byte                                                                                                                                          |            |

|            | Flags aff   | ected: O    | V,AC,CY                                                                                                                                                |            |

|            | Descripti   | on: ADI     | DC simultaneously adds the byte variable indicated, the carry flag and the                                                                             |            |

|            | Accumul     | ator con    | tents, leaving the result in the Accumulator ( $A = A + byte + CY$ ). The carry and                                                                    |            |

|            | auxiliary   | -carry or   | bit flags are set, respectively. If $CY = 1$ prior to this instruction, CY is also                                                                     |            |

|            | added to    | A.          |                                                                                                                                                        |            |

|            | Addressi    | ng mode     | s supported for ADDC instruction :                                                                                                                     |            |

|            |             | -           | e: ADDC A,#data                                                                                                                                        |            |

|            |             |             | ADDC A, Rn                                                                                                                                             |            |

|            |             | U           | DDC A, address                                                                                                                                         |            |

|            |             |             |                                                                                                                                                        |            |

|            | • K<br>(ii) | LCAI        | ndirect: ADDC A, @Ri                                                                                                                                   |            |

|            |             |             | all, Transfers control to a subroutine                                                                                                                 |            |

|            |             | -           | l6 bit addr                                                                                                                                            |            |

|            | Flags aff   |             |                                                                                                                                                        |            |

|            | _           |             | : 3 byte(1 byte is opcode and other two bytes are the 16 bit address of the                                                                            |            |